交换网络

交换网络的基本概念

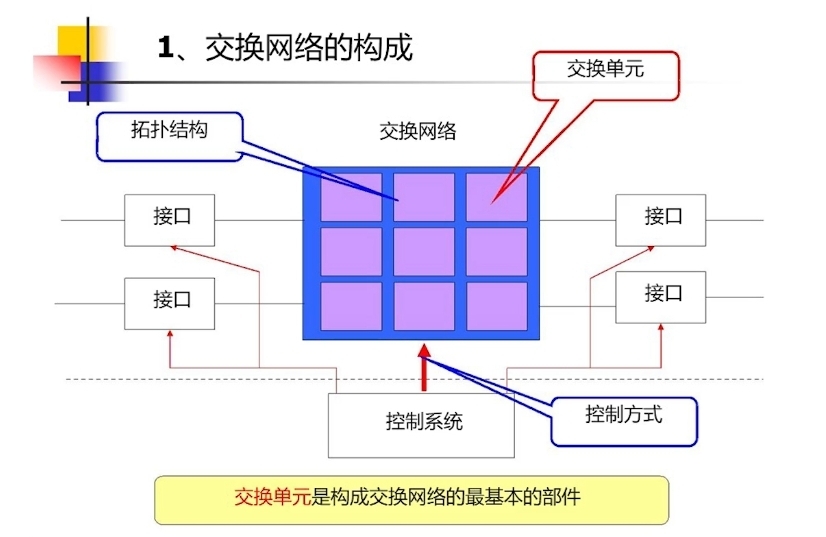

交换系统的根本就是交换网络 交换的最基本功能是在任意的入线与出线之间建立连接 构成交换网络的最小单位是交换单元 交换网络由交换单元按照一定的拓扑结构和控制方式决定(第二个三要素

CLOS网络

交换网络分类--单级交换网络和多级交换网络

单级交换网络:交换网络入线到出线只经过一个交换单元,并且同一级多个交换单元构成时,不同交换单元入线与出线之间可建立连接

多级交换网络: 1. 所有入线都只与第一次级交换单元链接 2. 所有第一级交换单元都只与入线第二季级交换单元链接 3. 依次类推

内部阻塞

多级交换才会出现内部阻塞

多级交换相比于单级交换

缺点:

- 两级交换网络的每一对出入线连接需要通过两个交换单元和一条级间链路,增加了控制交换单元和搜寻空闲链路的难度

- 两级交换网络中,任何时候在一对交换器间只有一对出入线接通(即阻塞时回因交换链路的占用而无法,同一个交换单元的任何其他入线无法再与已经建立好连接的出线单元建立任何链接,因为两个交换单元链路只有一条)

- 级数越高,成本越高

优点: 一般而言交换网络中的级数越高,建立链接的路径越多,阻塞的机会越少,链接能力越强。

无阻塞的三种概念

- 严格无阻塞网络:无论何时何种状态,任何时刻都可以在交换网络中建立一个连接,只要这个连接的起终点是空闲的

- 可重排无阻塞网络: 无论何时何种状态,都可以在一个交换网络中直接或对已有的连接重选路由来建立一个连接,只要这个连接的起点和终点是空闲的

- 广义无阻塞网络: 指一个给定的网络存在着固有的阻塞可能,但存在一种选路方法, 使所有阻塞均可以避免

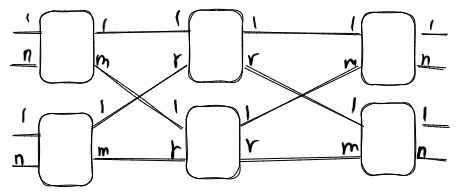

CLOS网络

三级的网络参数记为: \[C(m,n,r)\] 其中m,n,r都是整数,他用来描述这样一种CLOS网络:两边各有r各对称的m*n矩形交换单元,中间是m个r*r个的方形交换单元

目标:交叉点数随入、出线增长较慢的交换网络 CLOS做到了什么:对于较大的N,能够设计一种无阻塞网络,其交点增长速度小于\[ N^{\xi+1} (0<\xi<1) \] 也就是说,使用CLOS网络既可以减少交点数,又可以做到无阻塞

三级CLOS网络严格无阻塞条件:在最不利的情况下,中间级最多会出现\[(n-1)\times2\] 阻塞,因此中间级至少满足有\[m\ge2n-1\] 才是严格无阻塞。 (最不利情况推导:输入侧目标交换单元除了最不利情况的目标输入线没被占用,其他的输入线均与不同的中间级交换单元链接,需要(n-1)个交换单元;输出侧目标交换单元除了最不利情况的目标输入出线没被占用,其他链路均被不同的交换单元占用,又需要(n-1)个交换单元;a与b进行交链接需要一个交换单元。固最差情况需要2n-1个交换单元)

三级CLOS网络可重排无阻塞条件:对于三级CLOS网络C(m,n,r),如果m>=n,则该网络可重排无阻塞 这种条件下通过交换单元对链路交换,总能解除阻塞状态

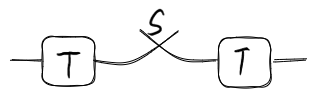

TST网络

TST网络是在电路交换系统中经常使用的一种交换网络,它是三级交换网络,两侧为T接线器,中间一级为S接线器,S级的出入线数决定于两侧T接线器的数量。

| 类别 | 目的 |

|---|---|

| 第1级T接线器 | 负责输入母线的时隙交换 |

| S接线器 | 负责母线之间的空间交换 |

| 第2级T接线器 | 负责输出母线的时隙交换 |

TST网络类型有两种,由T交换器控制方法决定: 1. 第一个T交换器输入控制,第二个T交换器输出控制 2. 第一个T交换器输出控制,第二个T交换器输入控制 S接线器是控制方式不限 (输入控制指的是控制写入,顺序读出,输出控制指的是顺序写入,控制读出)

为简便控制,一般将两个方向的内部时隙设置为具有一定对应关系,一般相差半帧,又称为反相法。 也可以采用奇偶控制。

TST网络以并行方式工作,所以串行数据进入前要进行串并变换。 由于常用编码为PCM一次群编码,需要通过时分复用将其由串行转换为并行。 目的:在高复用度情况下,不使码速过高,易于实现高速传输。

DSN网络

- 待定

BANYAN网络

(banyan网络类似树形结构,每一级与前面一级的关系类似于二分选择。)

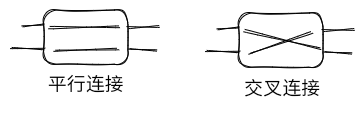

一个banyan网络是由多个电子开关构成,这种电子开关具有两种状态:平行连接和交叉连接,这样的电子开关又被称为2X2交换单元。

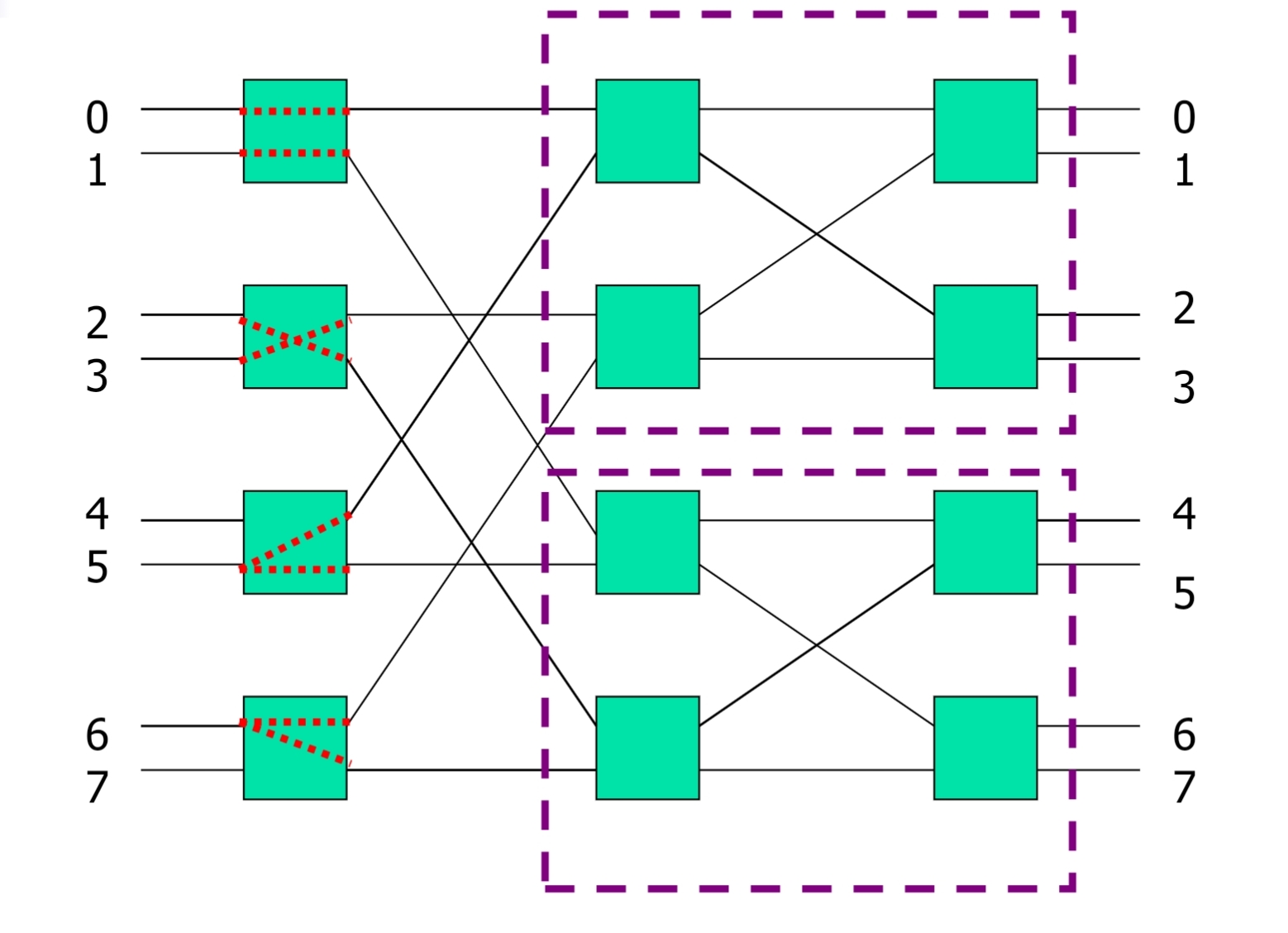

2X2交换单元可以构成一个4X4的二级交换网络,每增加一级可以扩大交换网络。

2X2交换单元可以构成一个4X4的二级交换网络,每增加一级可以扩大交换网络。

BANYAN网络特点

- 按规律可以用较小的BANYAN网络构成交大的BANYAN网络。

- 用两组N*N的网络,加上N个2*2 交换单元,构成 2N*2N 的网络。

出/入线、级数、交换单元数的关系

N*N网络级数: \[M=log^2N\] N*N网络单元数:\[(N/2) log^2N\] BANYAN网络的任何一条入线与任何一条出线之间都有一条路径并且仅有一条路径,该网络具有唯一路径特性 BANYAN网络不是CLOS网络,他不符合CLOS网络的无阻塞条件,当一个8X8BANYAN网络在特定情况下会同时选择相同的中间级交换单元,这个单元到达目标交换单元只有一条链路,于是发生内部阻塞。此时BANYAN网络不满足可重排无阻塞。这种内部阻塞会随着阵列级数的增加而增加。 解决办法: 1. 限制入线上的信息量或加大缓冲存储器。内部阻塞是在2X2交换单元的两条入线上要向该单元同一个出线发送信元时产生,在最坏的情况下,这个概率是1/2。 2. 通过增加多级交换网络的级数来消除内部阻塞。要温柔全消除内部阻塞,级数至少需要\[2log_{2}N-1 \] 3. 增加BANYAN网络的平面数,构成多通道交换网络 4. 使用排序-BANYAN网络

排序-BANYAN网络

只要BANYAN网络同时输入的全部数据块的出线地址单调排了,则不存在内部阻塞,因此在BANYAN网络前加入了排序网络。

排序网络

一个N输入排序网络,也被称为N-排序器,即给定输入\[I=\left \{ i_{0},i_{1},···,i_{N-1} \right \}

\] 形成输出\[O=\left \{

o_{0},o_{1},···,o_{N-1} \right \} ,且o_{0}\le o_{1}\le ···\le

o_{N-1}\]

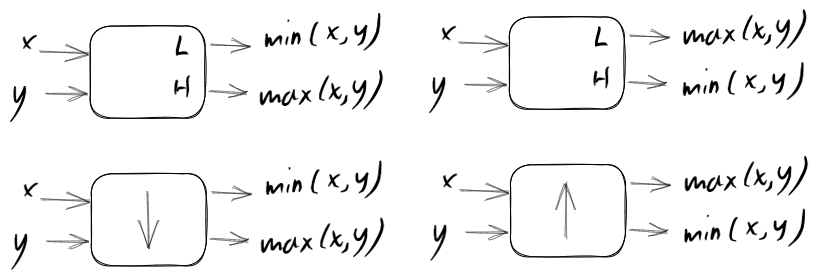

一种常见构成排序网络的开关是2-排序器,又称为2X2比较器,也称BATCHER比较器。由它构成的排序网络被称为BATCHER排序网络

(在整理排序网络原理的时候又折腾了一些相关的东西,这里是链接→排序网络与双调排序)

排序网络与交换网络采用洗牌连接,构成8X8交换网络。

排序-BANYAN网络消除了内部阻塞,但是不能消除出线阻塞,为此除了可以采用输入或输出缓冲排队的方法,还可以考虑在排序网络与BANYAN网络间构建反馈线,当出线标记相同的信元时,选择级别高的信元放行,另一个送回输入端重新排序。

(在整理排序网络原理的时候又折腾了一些相关的东西,这里是链接→排序网络与双调排序)

排序网络与交换网络采用洗牌连接,构成8X8交换网络。

排序-BANYAN网络消除了内部阻塞,但是不能消除出线阻塞,为此除了可以采用输入或输出缓冲排队的方法,还可以考虑在排序网络与BANYAN网络间构建反馈线,当出线标记相同的信元时,选择级别高的信元放行,另一个送回输入端重新排序。